## 浙江省 2017 年 4 月高等教育自学考试

## 数字电路试题

课程代码:02344

请考生按规定用笔将所有试题的答案涂、写在答题纸上。

## 选择题部分

## 注意事项:

1. 答题前,考生务必将自己的姓名、准考证号用黑色字迹的签字笔或钢笔填写在答题纸规定的位置上。

2. 每小题选出答案后,用 2B 铅笔把答题纸上对应题目的答案标号涂黑。如需改动,用橡皮擦干净后,再选涂其他答案标号。不能答在试题卷上。

## 一、单项选择题(本大题共 10 小题,每小题 1 分,共 10 分)

在每小题列出的四个备选项中只有一个符合题目要求的,请将其选出并将“答题纸”的相应代码涂黑。错涂、多涂或未涂均无分。

1.  $[110110]_2$  等于十六进制数

- 36

- 54

- 66

- 312

2. 函数  $F(A, B, C) = \overline{AB}(A+C)$  的最小项个数是

- 1

- 2

- 4

- 7

3. CMOS 或门的多余输入端可以

- 接地

- 接电源

- 悬空

- 剪断

4. 负逻辑的“与”等效正逻辑的

- 与非

- 或非

- 与

- 或

5. 8 位输入的二进制译码器输出位数是

- 3

- 8

- 16

- 256

6. 实现二进制数加法  $1001+1000$  需要全加器数量

- 1

- 2

- 4

- 8

7. 要实现 J-K 触发器  $Q^{n+1} = Q^n$  可以设定输入

- $J=K=1$

- $J=K=0$

- $J=\overline{K}=1$

- $J=\overline{K}=0$

8. 100 进制数器需要触发器个数至少是 [www.zjzikao.org](http://www.zjzikao.org)

A. 100

B. 12

C. 7

D. 5

9. 用 555 构成的施密特触发器的回差电压是

A.  $V_{cc}/2$

B.  $V_{cc}/3$

C.  $V_{cc}/4$

D.  $V_{cc}/5$

10. 设 A/D 转换的量化单位为  $\Delta$ , 则量化误差一定

A.  $\leq \Delta$

B.  $\leq \Delta/2$

C.  $\leq \Delta/3$

D.  $\leq \Delta/4$

## 非选择题部分

注意事项:

用黑色字迹的签字笔或钢笔将答案写在答题纸上, 不能答在试题卷上。

### 二、填空题(本大题共 10 小题, 每小题 1 分, 共 10 分)

11. VHDL 的结构体用于描述设计单元内部的 \_\_\_\_\_。

12. 若  $m_3$  表示为  $\bar{A}BC$ , 则  $m_6$  表示为 \_\_\_\_\_。

13. CMOS 反相器是由 P、N 两种沟道的 MOS 管按照 \_\_\_\_\_ 形式连接构成的。

14. 超前进位加法器的进位是由 \_\_\_\_\_ 直接产生的。

15. 当  $Y=A \oplus B=0$  时, A、B 关系是 \_\_\_\_\_。

16. 令 J-K 触发器的输入  $J=\bar{K}=A$ , 则电路转换为 \_\_\_\_\_ 触发器。

17. n 个 D 触发器构成扭形计数器的结构特点是 \_\_\_\_\_。

18. 256×8 位 RAM 扩展为 1024×16 位需要 \_\_\_\_\_ 片。

19. 多谐振荡器输出脉冲中除基波外, 还含有极丰富的 \_\_\_\_\_。

20. D/A 转换器的分辨率约是 0.03, 则转换器有 \_\_\_\_\_ 位。

### 三、分析题(本大题共 8 小题, 每小题 5 分, 共 40 分)

21. 写出十进制数 0 ~ 9 的 5211BCD 码。

22. 用公式法证明等式:

$$AB + \bar{A}\bar{C} + BC = AB + \bar{A}C$$

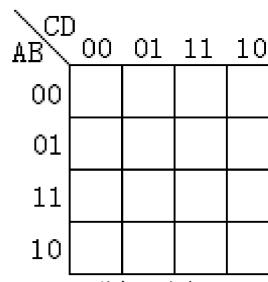

23. 画出逻辑函数  $F(A, B, C, D) = A \cdot \overline{B + \bar{C} + \bar{A}D}$  的卡诺图。

题 23 图

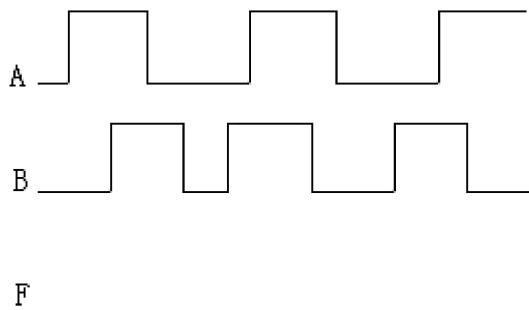

24. 已知真值表及其输入 A、B 波形, 画出相应输出 F 波形。

| A | B | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

题 24 图

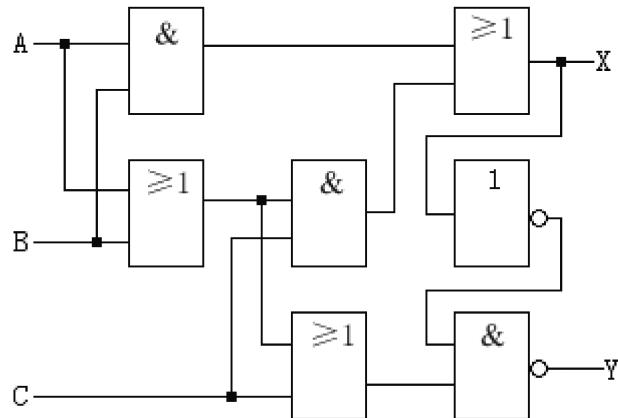

25. 分析给定组合逻辑电路, 输入为 A、B、C, 写出输出 X、Y 表达式(不要求化简)。

题 25 图

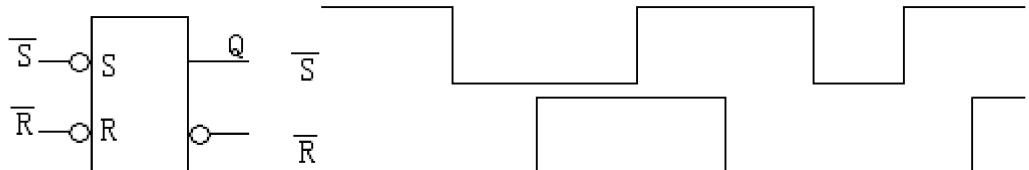

26. 基本 R-S 触发器的符号如图所示, 要求根据输入波形画出对应的输出波形。

Q

$\bar{Q}$

题 26 图

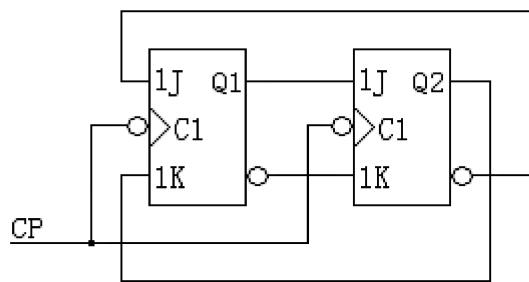

27. 分析如图所示逻辑电路图,画出状态图( $Q_1Q_2$  排列,起始状态 00),并说明为几进制计数器。

题 27 图

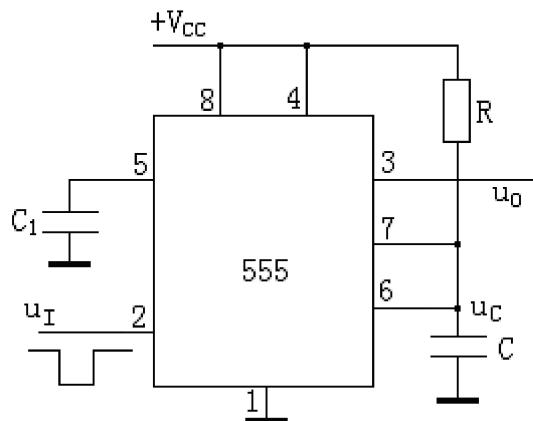

28. 在图示单稳态触发器中暂稳态持续时间  $t_w = 6.6\mu s$ , 电容值  $C = 0.01\mu F$ , 估算电路中的电阻阻值,并说明电容  $C_1$  的作用。

题 28 图

四、设计题(本大题共 5 小题,每小题 8 分,共 40 分)

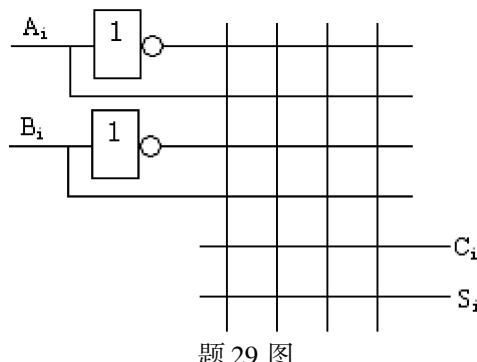

29. 设计半加器。要求列出真值表( $C_i$ 表示进位,  $S_i$ 表示和),画出 ROM 存储矩阵结点连接图。

| $A_i$ | $B_i$ | $C_i$ | $S_i$ |

|-------|-------|-------|-------|

| 0     | 0     |       |       |

| 0     | 1     |       |       |

| 1     | 0     |       |       |

| 1     | 1     |       |       |

题 29 图

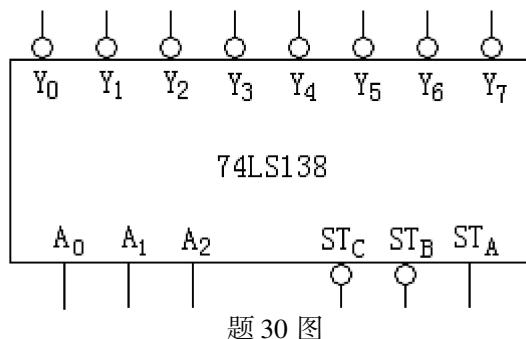

30. 用如图所示一片 3-8 线译码器及适当门电路实现函数  $F(A, B, C) = \overline{AB} + \overline{BC} + \overline{AC}$ 。要求写出函数标准与或式, 画出连线图。

题 30 图

31. 化简带有约束的函数, 并用最少的与非门实现, 画出逻辑图。

$$\begin{cases} F(A, B, C, D) = AB\bar{C} + A\bar{B} \cdot \bar{C} + \bar{A} \cdot \bar{B}C\bar{D} + A\bar{B}C\bar{D} \\ \bar{A} \cdot \bar{B} \cdot \bar{C} \cdot \bar{D} + ABCD = 0 \end{cases}$$

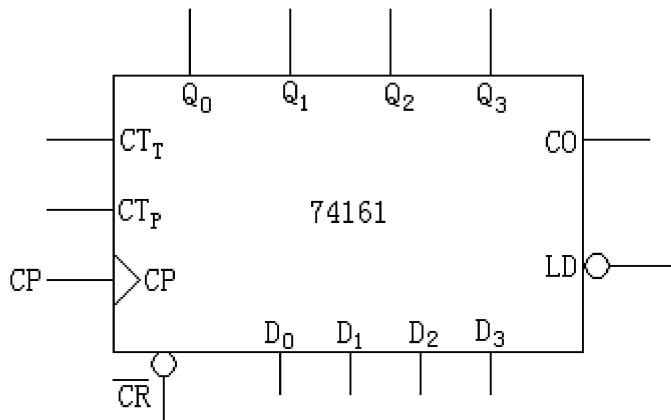

32. 利用 74161 异步清零功能实现十进制计数, 画出状态图(按  $Q_3Q_2Q_1Q_0$  排列)和连线图。

74161 的状态表

| 输入              |                 |        |        |      |       |       |       | 输出    |             |             |             |             |      |

|-----------------|-----------------|--------|--------|------|-------|-------|-------|-------|-------------|-------------|-------------|-------------|------|

| $\overline{CR}$ | $\overline{LD}$ | $CT_P$ | $CT_T$ | $CP$ | $D_0$ | $D_1$ | $D_2$ | $D_3$ | $Q_0^{n+1}$ | $Q_1^{n+1}$ | $Q_2^{n+1}$ | $Q_3^{n+1}$ | $CO$ |

| 0               | x               | x      | x      | x    | x     | x     | x     | x     | 0           | 0           | 0           | 0           | 0    |

| 1               | 0               | x      | x      | ↑    | $d_0$ | $d_1$ | $d_2$ | $d_3$ | $d_0$       | $d_1$       | $d_2$       | $d_3$       |      |

| 1               | 1               | 1      | 1      | ↑    | x     | x     | x     | x     | 计数          |             |             |             |      |

| 1               | 1               | 0      | x      | x    | x     | x     | x     | x     | 保持          |             |             |             |      |

| 1               | 1               | x      | 0      | x    | x     | x     | x     | x     | 保持          |             |             |             | 0    |

题 32 图

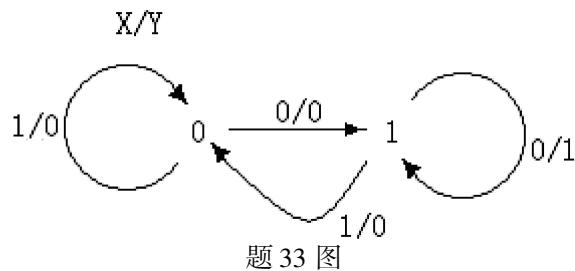

33. 给定串行数据检测器的状态图(起始状态为“0”状态),用上升沿触发的边沿 D 触发器和适当门电路设计该电路。要求写出逻辑方程,画出逻辑电路图。